# The DFM Advantage

A review of predictive engineering progress.

Happy T. Holden

s the capabilities of electronics products steadily increase, so does a corresponding increase occur in the complexity of their packaging. Electronic design automation (EDA) tools and concurrent engineering are primary drivers of this phenomenon. An effective technique to feed back manufacturing experiences and wisdom has been lacking because the data flows in only one direction—from design to manufacturing. Hewlett Packard (Loveland, CO) has spent several years developing a predictive engineering program for fabricating bare PCBs. Known as design for manufacturability (DFM), the program addresses the increasing complexity brought on by SMT, the need for improved performance, and cost reduction. The program is essentially TQM applied to R&D.

## Why DFM?

There are five reasons why DFM is essential to the design of cost-effective electronic products:

- Seventy-five percent of the manufacturing costs of a product are determined by its design drawings and specifications.

- Sixty percent of the product's manufacturing costs

| Board design stage                                        | Time -                                   |

|-----------------------------------------------------------|------------------------------------------|

|                                                           | Prototype & manufacturing                |

| -                                                         |                                          |

| -                                                         |                                          |

| -<br>Shaded area represents<br>region of cost flexibility |                                          |

|                                                           |                                          |

|                                                           | planning design design circuit<br>layout |

Figure 1. Early application of DFM results in greater cost savings.

are determined in the first stages of design, at a time when only 35% of the design cost has been applied.

- Products have become extremely intricate, primarily because the sophisticated EDA tools supporting product design are so easy to use that complex features can be invoked by the flip of a switch. Unfortunately, manufacturing yields respond inversely to complex design.

- The opportunity to reduce overall product costs is greatest early in the design cycle. This applies not only to partitioning, but also to selecting specific manufacturing technologies (Figure 1).

- DFM provides a common language that allows manufacturing and quality engineers to communicate with design and R&D engineers by defining *producibility* as an intrinsic design characteristic. Producibility scoring forms an objective baseline that encourages a team approach to designing and manufacturing a quality, cost-competitive product.

# DFM as an Infant Technology

DFM was created by Professors Peter Dewhurst and Geoffry Boothroyd in 1983. Their pioneering work on mechanical assembly, based on an easily mastered scoring procedure, provided the foundation for design methodology. Their approach analyzed each part of a mechanical assembly from the standpoint of:

- . necessity of existence of each separate part

- . ease of handling, feeding, and orienting

- . ease of assembly.

H-P applied these principles to its electronics products in 1985 and has used it in conjunction with the GE-Hitachi Assembly Evaluation Methodology ever since. The Boothroyd approach to DFM is based on kinematic scoring. The electronics area, however, is more closely akin to the flow of fluids in pipes than to mechanical assembly, and therefore the DFM approach to PCB and ASIC applications are better scored thermodynamically. Traditional thermodynamics calculations are quite cumbersome, involving the use of pseudo-independent variables such as Reynold's number and Fanning's friction factor to establish the relationship of real variables. The measure for producibility in electronics manufacturing is a similar pseudo-independent-created variable, which can be readily handled by software programs.

Mentor Graphics Corp. (San Jose, CA) and Mitron (Beaverton, OR) recently articulated several Framework softwares that complement aspects of concurrent engineering by computerizing producibility relationships. As shown in Figure 2, the Predictive Engineering Framework provides for design planning, partitioning, simulation, and other "what if" tradeoffs. The DFM software is fed by the Manufacturing Framework, This software environment was one of four objectives in H-P's PCB manufacturing program. The other three goals were:

- to define a scoring methodology for printed circuit board producibility

- to collect best practices, electrical performance information, and manufacturing capabilities into a DFM manual

- . to provide a seamless electronic transfer environment for electronic designs from R&D to manufacturing.

# The H-P DFM Project

In 1989, several existing DFM programs were evaluated. The oldest, then in use at the Defense Systems Group of Texas Instruments (TI, Austin, TX), was commercialized by Mentor Graphics. A second program, developed by AT&T Bell Labs (Hopewell, NJ), used Unit Cell Concept software in predicting tradeoffs for CAD autorouters. At IBM (Austin, TX), a system called the Design Report Card was developed for SMT assembly.

The H-P DFM program is like these in that it has a scoring methodology for producibility. It differs in that it creates a DFM manual that documents the following performance objectives for the manufacture of bare PCBs:

- to mount all the components in the bill of materials

- . to interconnect the components with a technology set  $% \left( {{{\bf{x}}_{i}}} \right)$

- . to provide the proper environment for the electrical signals of the interconnects.

The bottom line is to provide design engineers and PCB layout people with a quick way to evaluate the tradeoffs between performance objectives and PCB costs. Producibility scoring is needed since one must have at least a general idea of manufacturing yields before costs can be estimated. The key metrics developed to evaluate price/performance tradeoffs are:

- the design density index (DDI), which determines alternate technology sets that can interconnect all the inventoried parts for a PCB

- the complexity index (CI), which characterizes the aggregate complexity of elements such as board size, layers, holes, and traces, so that first-pass yield can be determined

- the relative cost index (RCI), an artificial currency indicating the magnitude of price changes between two or more design alternatives.

Software was developed to illustrate the interactions of these three metrics with electrical performance.

# An Example of the DFM Process

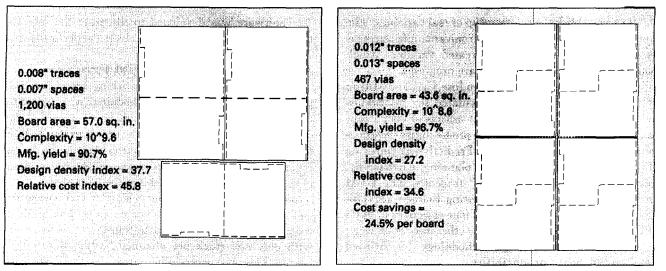

In early 1989, H-P was working on a low-cost personal laser printer. DFM methodology was applied to determine if more cost savings could be wrung out of the design. Figures 3a and 3b show the design of the PCB in the unit before and after DFM metrics. Among the design criteria that had to be met were maximum size and location of the connectors that plugged into the laser engine.

The DDI indicated that a simpler technology set could be used to wire up the components. The original six-layer layout was changed to four-layer construction with only one track per channel (0.012" line/0.013" space). This was successfully routed, along with reduced vias and balanced plating areas. A DDI analysis showed that a smaller board size and the removal of some of the small-scale ICs would be advantageous. The addition of one more ASIC increased the boards per panel from six to eight. When the small-scale ICs were replaced with a very simple gate array ASIC in a QFP, 13 sq. in. of board real estate were saved. The ASIC designers asked why anyone would want to use such a simple gate array. They didn't understand that the ASIC's cost was trivial compared to the cost of the epoxy fiberglass substrate.

At the end of the DFM process, the PCB had been greatly simplified. It was reduced from 57 to 43.6 sq. in.; six layers were shaved to four; connectivity went from 8/7-mil lines and spaces to 12/13; vias were reduced from 1,200 to 467; and complexity was cut by an order of magnitude. The result was an RCI reduction of 24.5%.

Extended over the long lifespan of the printer, the 24.5% RCI reduction saved millions of dollars. Twentyfive percent is a typical savings level attributable to DFM when the program is applied at the end of the design cycle. Greater savings result when the program is applied at the very start of the design process (partitioning).

Figure 2. New frameworks for design.

# Manufacturability

Figures 3a and 3b. PCB design and metrics before and after DFM.

# **Future Activities**

Hewlett Packard plans to incorporate other existing DFM concepts into its manufacturing software, enabling the company to create a version of the Design Report Card. This will allow all fabrication and assembly to be included in the tradeoffs. Software will eventually be merged into global partitioning methodologies such as Nanyang Technical University's (NTU, Singapore ) or MCC's (Austin, TX) System Performance Evaluation and Comparison.

H-P, IBM, AT&T, TI, NTU, and MCC are all working on parts of the DFM puzzle. A Predictive

# Manufacturability

Engineering Framework is needed to allow them to work in concert. Success depends on the manufacturing sector's ability to characterize its processes and keep them in statistical control. It's critical for the design sector to take ownership of the measures of producibility.

# Bibliography

- Boothroyd, Geoffry, and Peter Dewhurst. "Design for Assembly." Dept. of Mechanical Engineering, University of Massachusetts, Amherst, MA, 1983.

- Hawiszczac, Robert. Integrating Design for Producibility into a CAE Design Environment. Nepcon East, June 1989.

- Mantay, M. K., L. A. Range, and L. N. Schoenberg. "Optimizing Autorouting Boosts PCB Manufacturability." *Electronics Packaging & Production*, June 1991.

- Hume, H., R. Komm, and T. Garrison. *Design Report Card: A Method Measuring Design for Manufacturability.* Surface Mount International, September 1992.

- Bansal, Sam. "A New Framework *for* Concurrent Engineering Based on a Deterministic Model." Position paper, GINTIC Institute of Manufacturing Technology, NTU-Singapore, April 1993.

- Sandborn, Peter. A Software Tool for Technology Tradeoff Evaluation in Multichip Packaging. IEEE/CHMT's IEMT 1991 Symposium.

Holden, Happy. The PC Board Design Process: Where Design for

Manufacturability Will Improve Performance. IEEE/CHMT's IEMT Symposium, 1991.

Holden, Happy. Zero Defect Manufacturing: A Focus on the Key Philosophies. Pronic 1990, Paris France.

# Acknowledgements

The author would like to thank the following individuals for their engineering creativity in developing the PCB DFM methodologies: Bill Tani, DFM consultant (Santa Clara, CA); Paul Henderson, Hewlett Packard, (Palo Alto, CA); Tim Rodgers, Hewlett Packard, (Loveland, CO); Clyde Parrish, Continental Circuits. (Phoenix, AZ); and Julie Connell, Hewlett Packard, (Santa Clara, CA).

Happy T. Holden is senior technical *contributor at* Hewlett *Packard Co.*, Loveland CO.

*This paper* was originally Presented *at* Surface Mount Interns. *tional, September 1993,* San Jose, CA.

Happy Holden will teach a class on design for manufacturability at the Midwest Electronics Expo, Minneapolis Convention Center, Minneapolis, MN, May 9, 1994.