# **Technical Article**

# Electrically Mediated Plating of Semiconductor Substrates, Chip Scale Packages & High-density Interconnect PWBs

By E.J. Taylor, J.J. Sun, B. Hammack, C. Davidson & M.E. Inman

This paper describes a process for low-cost plating of electronic interconnects for integrated circuits (IC), chip scale packages (CSP), and high-density interconnect printed wiring boards (HDI-PWB). In contrast to traditional chemical mediation of plating processes, the electrically mediated process does not rely on difficult-tocontrol leveling additives, such as brighteners and/or levelers. The methodology for selection of the electric mediation parameters is based on an understanding of the interactions of an "electrodynamic diffusion layer" with microprofiles and macroprofiles to control the metal distribution. Data for plating of sub-micron trenches, 30 to 75 micron microvias, and highaspect-ratio PTHs is presented. In addition to simplicity and robustness of the electrically mediated approach, data demonstrating the ability to metallize and planarize with minimal overplate is presented. The ability to plate/planarize is important for: (1) reducing or eliminating chemical mechanical polishing of ICs, (2) fabricating stacked microvias for CSPs, and (3) finepitched interconnects for HDI-PWBs.

The continuing trend toward miniaturization of consumer electronics is presenting considerable technological challenges to all segments of the electronics industry. Specifically, in advanced integrated circuits (ICs), copper interconnections are replacing aluminum.<sup>1,2</sup> Because the performance capabilities and miniaturization of IC devices are proceeding at a rate significantly faster than the printed wiring board technology required to interconnect them,<sup>3</sup> the need for chip scale packages (CSPs) and high-density inter-

# Nuts & Bolts: What This Paper Means to You

Features on printed wiring boards (PWBs) and interconnects are getting smaller and smaller . . and smaller. Maintaining uniformity and leveling in copper plating of these tiny features with the tools we have is getting harder and harder . . and harder. Interest in pulse plating and all of its variations is getting more intense by the day. Here, the authors consider just what pulse can do in meeting the demands of today's PWB designs.

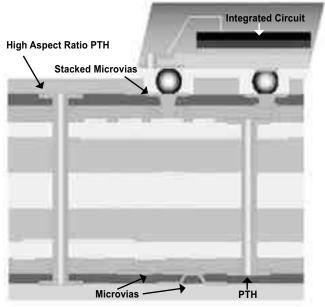

Fig. 1-Schematic of advanced electronic package.

connect printed wiring boards (HDI-PWBs) has emerged. As depicted in Fig. 1, the CSP and HDI-PWB provide the z-axis interconnection between the IC and the PWB.

The challenge of plating electronic interconnects is one of leveling or throwing power (*i.e.*, the uniform deposition of a conductor into microprofiles<sup>4</sup>). There are two types of leveling: geometric leveling and true leveling.

Geometric leveling results from a uniform or primary current distribution. Consequently, the plating rate must be very slow. Geometric leveling only occurs when the deposit is at least as thick as the depth of the microprofile, so the overplate is considerable. Geometric leveling is impractical for fabrication of electronic interconnects.

True leveling results from the preferential adsorption of a specific leveling additive or additives on the highcurrent-density areas (*e.g.*, peaks or corners of the microprofile). True leveling requires precise control of these additives, also known as levelers and brighteners.

In conventional direct-current (DC) plating of plated through-holes (PTHs) for the PWB industry, leveling additives are incorporated in the plating bath to improve the throwing power and to yield a fine-grained deposit.<sup>5,6</sup>

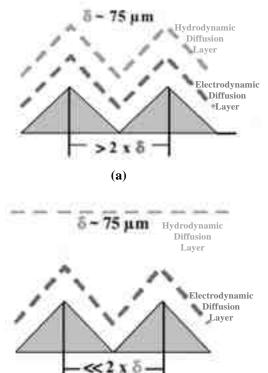

Fig. 3—Relationship between the hydrodynamic diffusion layer and the electrodynamic diffusion layer for (a) macroprofile and (b) microprofile.

**(b)**

Considerable challenges exist, however, for extension or insertion of PTH electroplating processes to the smaller microvias and IC features. Specifically, the proprietary chemistries used in "conventional" and "high-throw" baths do not necessarily provide acceptable results for smaller interconnect features,<sup>7</sup> and proprietary chemical formulations must be optimized for different feature sizes.<sup>8</sup> Furthermore, bath maintenance and control issues associated with the leveling additives are exacerbated at HDI, CSP and IC feature sizes.

To meet the plating challenge of advanced electronic interconnects, non-DC plating processes have recently received considerable interest.  $^{9\cdot13}$

While these non-DC processes have been referred to by a variety of names (*e.g.*, periodic reverse plating and pulse reverse plating), they all utilize brighteners and/or levelers and are, therefore, a form of true leveling.

Consequently, the challenge of precise control of leveling additives remains. In addition, these previous studies<sup>9-13</sup> have used one

Fig. 5—Generalized waveform for high-aspect-ratio PTHs and microvias.

Fig. 6—Generalized waveform for IC features.

Fig. 7—Electrically mediated plating of PTH.

set of waveform parameters, characterized by a long forward or cathodic pulse followed by a short reverse or anodic pulse.

As suggested from fundamental considerations, however,<sup>14</sup> changes in waveform parameters should have a substantial impact on the copper plating of interconnect features. In addition, Rehrig and Mandich<sup>15</sup> studied the effect of pulse plating parameters on throwing power. They suggested that "simple electronic manipulation of the pulse waveform" could be used to "tune" the electro-deposition process and replace the complicated brightener/leveler chemistries.

Recently, copper plating for electronic applications without brighteners and levelers has been reported.<sup>16-18</sup> This process is termed *electrically mediated copper plating*, in contrast to the conventional chemically mediated approach using leveling additives. In this paper, we present further results using electrically mediated copper plating of electronic interconnects.

# Approach

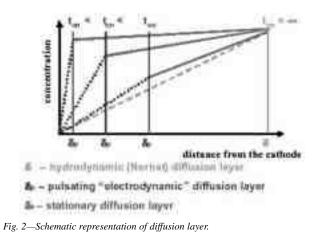

In the electrically mediated approach, the forward on-time/peak current and reverse on-time/peak current are tuned to plate specific electronic features. The rationale for selecting the process parameters is derived from the influence of a pulsating current on the hydrodynamic diffusion layer. As shown in Fig. 2, during pulse plating, a "duplex diffusion layer" develops. The duplex diffusion layer consists of a stationary layer and an inner pulsating layer. By assuming linear concentration gradients, Ibl<sup>19,20</sup> derived the following relationship between the pulsating diffusion layer and the on-time of the pulse:

$$\delta_{\rm p} \approx (2\mathrm{Dt}_{\rm on}) \tag{1}$$

where D is the diffusion constant,  $t_{on}$  is the on-time of the pulse and  $\delta_p$  is the pulsating diffusion layer. More recently, using a similar duplex diffusion layer approach, the same relationship was derived for "pulse-with-reverse" plating.<sup>21</sup> Because the pulsating diffusion layer is determined by the on-time of the pulse, we refer to it as the "electrodynamic diffusion layer."

As shown in Fig. 3, proper selection of the electrodynamic diffusion layer can convert a macroprofile to a smaller macroprofile or convert a microprofile to a smaller microprofile. In order for diffusion processes and thereby the electrodynamic diffusion layer to influence the plating process, however, mass transport effects must be significant during the duration of the pulse. The time required for the concentration of reacting species at the interface to be depleted to zero is known as the transition time,  $\tau$ , and is given by the Sand equation:

$$\tau \approx ((nF)^2 C^2 D)/2i_{or}^2$$

<sup>(2)</sup>

Fig. 8—Electrically mediated plating of highaspect-ratio PTH.

Fig. 9—Electrically

mediated plating of microvias for HDI-

PTH.

Cu Rhickness <sup>26</sup>.00045

| Size     | Aspect<br>Ratio | Throwing<br>Power |

|----------|-----------------|-------------------|

| 0.075 mm | 1:1             | 105%              |

| n n      |                 |                   |

|          | M               |                   |

|          |                 |                   |

|          | 2 F.            |                   |

|          | 5               | 2                 |

|          | G               |                   |

|          | r<br>S<br>S     |                   |

where n is the number of electrons, F is Faraday's constant, C is the bulk concentration of the reacting species, and  $i_{on}$  is the pulse current. Consequently, mass transport effects influence the plating process when the transition time is significantly less than the on-time:

$$\tau \ll t_{a}$$

(3)

While the theoretical framework is not sophisticated enough to allow *a priori* determination of waveform parameters, the above

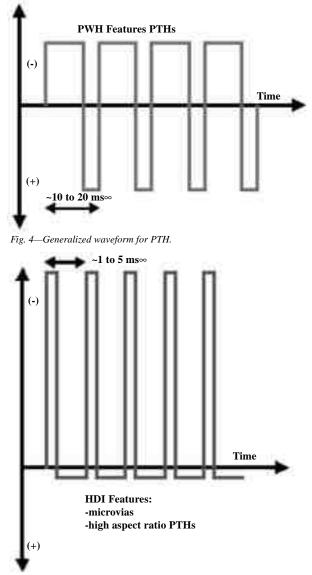

discussion and previous work<sup>16-18</sup> provide substantial guidance. Specifically, low-aspect-ratio PTHs are macroprofiles and require a relatively long forward on-time followed by a relatively short reverse on-time. The sum of the forward on-time and reverse on-time, as well as any off-times, is approximately 10 to 20 msec, or 100 to 50 Hz. The general form of the electrically mediated process waveform for PTHs is presented in Fig. 4.

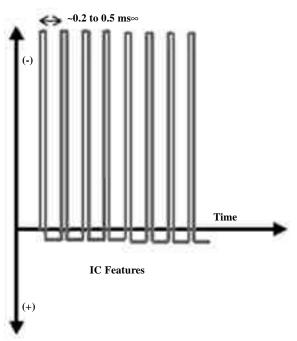

High-aspect-ratio PTHs, microvias, and IC features are microprofiles and require short forward on-time/high forward peak current, followed by a relatively long reverse on-time/low reverse peak current. For high-aspect-ratio PTHs and microvias, the sum of the forward on-time and reverse on-time, as well as any offtimes, is approximately 1 to 2 msec, or 1000 to 500 Hz. For IC features, the sum of the forward on-time and reverse on-time as well as any off-times, is approximately 0.2 to 0.5 msec, or 5000 to 2000 Hz. The general form of the electrically mediated process waveforms for high-aspect PTHs/microvias and IC features are presented in Figs. 5 and 6, respectively.

| Plating<br>Time    | 180<br>min                           | 180<br>min |

|--------------------|--------------------------------------|------------|

| 110A<br>(2011 PTH) | Secf 0.0007<br>Cu 0.0009<br>TP 120%  | ר ר        |

| 0.062<br>(4(1 PTH) | Suef 0.0019<br>Cir 0.0019<br>TP 100% |            |

Fig. 10—Electrically mediated plating of high-aspect-ratio BGA and low aspect ratio PTH.

Fig. 11-Electrically mediated plating of 30 mm microvia for CSP.

Fig. 12—Electrically mediated plating of 30 mm microvia for CSP, with process parameters adjusted to fill microvia.

# **Experimental Procedure**

An acid copper sulfate solution containing 60 g/L CuSO<sub>4</sub>, 9% by volume of  $H_2SO_4$ , 60 ppm Cl<sup>-</sup>, and 350 ppm polyethylene glycol (PEG) was used as the copper electroplating bath for all experiments. The chloride/PEG acts as a suppressor and is not difficult to control.<sup>22</sup> The plating bath does not contain difficult-to-monitor/ control additives such as brighteners and/or levelers. The plating bath temperature was 25°C (78°F).

For the HDI-PWB features, plating experiments were conducted on 20.3 x 45.7-cm (8 x 18 in.) panels of 0.318 and 0.635 cm (0.125 and 0.250 in.) thicknesses containing microvias, PTHs and ball grid arrays (BGAs). The plating line (vertical) consisted of a single panel flight bar with eductors oriented at 90° perpendicular, knifeedge agitation and mesh insoluble anodes. As described previously, the insoluble anodes offered potential advantages for reverse pulse plating.<sup>23</sup> For the CSP and IC features, plating experiments were conducted on 1.9 x 1.9 cm (0.75 in.) samples in a rotating electrode apparatus.

# Results

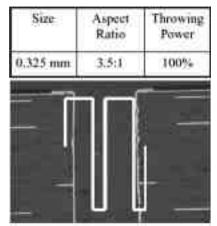

In Fig. 7, the results for the electrically mediated copper plating of a 3.5:1 aspect ratio PTH are presented. The waveform used was the long forward on-time/short reverse on-time at a frequency of approximately 50 Hz. The throwing power was approximately 100 percent.

In Fig. 8, the results for the electrically mediated copper plating of a 20:1 high-aspect-ratio PTH are presented. The waveform used was the short forward on-time/long reverse on-time at a frequency of approximately 500 Hz. The throwing power was approximately 100 percent. Further optimization of the electrically mediated process parameters is expected to yield the desired throwing power.

Fig. 13-Electrically mediated plating of 0.25, 0.50 and 0.77 mm IC feature.

In Fig. 9, the results for the electrically mediated copper plating of microvias for HDI-PWBs are presented. The waveform used was the short forward on-time/long reverse on-time at a frequency of approximately 500 Hz. The throwing power was approximately 100 percent.

In Fig. 10, the results for the electrically mediated copper plating of an HDI-PWB containing a high-aspect-ratio BGA and a lowaspect-ratio PTH are presented. The excellent throwing power and coverage results were obtained using the long forward on-time/ short reverse on-time at a frequency of approximately 50 Hz followed by the short forward on-time/long reverse on-time at a frequency of approximately 500 Hz.

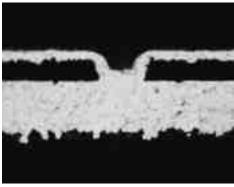

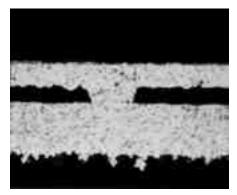

In Fig. 11, the results for the electrically mediated copper plating of microvias for CSPs are presented. The waveform used was the short forward on-time/long reverse on-time at a frequency of approximately 2000 Hz. The throwing power was approximately 100 percent. In Fig. 12, the process parameters were adjusted to fill the microvia. The ability to fill microvias is important to enable the stacked microvia designs illustrated in Fig. 1.

In Fig. 13, the results for the electrically mediated copper plating of IC features are presented. Good void-free filling for 0.25, 0.50 and 0.77  $\mu$ m IC features are obtained. Of particular note is the minimal overplate associated with the electrically mediated process.

#### Summary

An electrically mediated process for copper plating of electronic interconnects is described.<sup>24,25</sup> Specifically, copper plating PTHs and microvias for HDI-PWB, microvias for CSP and IC features ranging in size from 325 down to 0.25 µm. In contrast to conventional plating art based on brightening/leveling additives, the electrically mediated process is based on predictable knowledge.

The critical parameters of the electrically mediated process are forward and reverse on-times and forward and reverse peak currents. By understanding the influence of an electrodynamic diffusion layer on macroprofiles and microprofiles, the process parameters are tuned to the electronic interconnect feature of interest. As additional knowledge and experience is derived from the electrically mediated process, a library of process parameters will be developed. Consequently, as new electronic packages are required, the electrically mediated process parameters will be selected from a library of process parameters.

# Acknowledgment

The authors acknowledge the efforts of L. Gebhart for the design and construction of the experimental apparatus and plating line, and P. Miller for technical editing of the manuscript. The financial support of Faraday Technology, Inc. and Multilayer Inc. are gratefully acknowledged.

# References

- L. Zuckerman, "IBM to Make Smaller and Faster Chips— Second Breakthrough in a Week has Wide Uses," *The New York Times*, p. D1, September 22, 1990.

- D.C. Edelstein, Proc. 12<sup>th</sup> Int'l. IEEE VLSI Multilevel Interconnection Conf.," IEEE, Piscataway, NJ, 1995; p. 301.

- 3. R.D. Rust, *Proc. IPC Fall Meeting, TP IPC-TP-673*, IPC, Northbrook, IL, October 1987.

- 4. M. Paunovic & M. Schlesinger, *Fundamentals of Electrochemical Deposition*, Wiley Inc., New York, NY, 1998.

- 5. E. Yung, L. Romankiw & R. Alkire, *J. Electrochem. Soc.*, **136**, 206 (1989).

- 6. E. Yung & L. Romankiw, J. Electrochem. Soc., **136**, 756 (1989).

- S. Castaldi & D. Fritz, *IPC Printed Circuits Expo*, IPC, Northbrook, IL, April, 1998.

- D. Fritz, *IPC Printed Circuits Expo*, IPC, Northbrook, IL, April, 1998.

- 9. T. Pearson & J. K. Dennis, *J. Applied Electrochemistry*, **20**, 196 (1990).

- 10. S. Coughlan, Trans. IMF, 74, (May 1996).

- 11. R. van't Wout Hofland, "Going in Reverse," *PC FAB*, November 2000.

- 12. G. Milad & M. Lefebvre, "PPR Plating for HDI," *PC FAB*, September 2000.

- 13. R. Blake, D. DeSalvo & R. Retallick, "Pulse Plating," *PC FAB*, January 2000.

- 14. K.M. Takahashi & M.E. Gross, J. Electrochem. Soc., 146, 4499 (1999).

- D.L. Rehrig & N. Mandich, *Plating & Surface Finishing*, 86, 89 (December 1999).

- E.J. Taylor, J. Sun & M. E. Inman, *Plating & Surface Finishing*, 87, 68 (December 2000).

- 17. E.J. Taylor, J.J. Sun, M.E. Inman & L. Zhang, *IPC Printed Circuits Expo*, IPC, Northbrook, IL, April, 2000.

- E.J. Taylor, J.J. Sun & M.E. Inman "Electrically mediated Plating of Through-Holes & Microvias," *PC FAB*, March 2001.

- 19. N. Ibl, Surface Technology, 10, 81 (1980).

- J-C. Puippe & F. Leaman, *Theory & Practice of Pulse Plating*, AESF, Orlando, FL, 1986.

- 21. K. Yin, Surface & Coatings Technology, 88, 162 (1996).

- 22. R.D. Mikkola, Q.T. Jiang & B. Carpenter, *Plating & Surface Finishing*, **87**, 81 (March 2000).

- 23. S. Henny & H. Matejat "HDI Production Using Pulse Plating with Insoluble Anodes," *Circuitree*, February 2001.

- 24. E.J. Taylor, J. Sun & C. Zhou, U.S. patent 6,210,555 (2001).

- 25. E.J. Taylor, J. Sun & C. Zhou, U.S. patent 6,203,684 (2001).

# About the Authors

Dr. E. Jennings Taylor\* is the chief technical officer at Faraday Technology, Inc., 315 Huls Dr., Clayton, OH 45315. He founded the company to develop and commercialize innovative electrochemical technology using sophisticated charge-modulated electric fields. The company's intellectual property has been successfully transferred both to government agencies and large manufacturers in the form of process engineering technology and prod-

ucts. He holds a BA in chemistry from Wittenberg University, an MA in technology strategy and policy from Boston University, and MS and PhD degrees in materials science from the University of Virginia. He has published more than 70 technical papers and articles and holds 11 patents. He serves on the AESF Pulsed Electrodeposition Processes Committee and is chairman of the Research Board.

Jenny J. Sun is a project engineer at Faraday Technology, Inc. She has worked on numerous projects to establish the feasibility of using charge-modulated electric fields for electrodeposition and electrochemical machining technology. She holds a BS in materials science from the University of Science and Technology, Beijing, and an MS in materials science from Wright State University. She is a member of AESF and the Electrochemical Society, has published several papers in the areas of electrodeposition and electrochemical machining, and is coinventor on several patent applications.

Dr. Maria E. Inman is the research manager at Faraday Technology, Inc., where she supervises all R&D activities. She holds a BE (Hons.) in metallurgical and materials engineering and a PhD in materials engineering from the University of Auckland, New Zealand. Prior to joining Faraday Technology, she completed a two-year term as a post-doctoral research associate at the Center for Electrochemical Science and

Engineering at the University of Virginia. She is a member of NACE, AESF and the Electrochemical Society. She is co-inventor on several patent applications and is the author of numerous technical publications.

Dr. Craig Davidson is the Vice President of Technology at Multek's new Technology Center in Irvine, CA. The Technology Center is responsible for development of new materials, process technology and equipment for Multek worldwide, and provides advanced PWB fabrication, quick turn, and special projects to select customers. Dr. Davidson is experienced in the development and volume insertion of high-density interconnect and printed wiring boards; advanced surface mount assembly; and both first-level and secondlevel assembly of advanced packages (e.g., multi-die BGAs and RF-MCMs). He has numerous publications, three patents issued, and five patents pending.

Brad Hammack is the General Manager at Multek in Irvine, CA, where he manages the quick-turn prototype facility, process development, high-performance materials, and advanced applications in PWB fabrication. His previous experience includes more than a decade at IBM, where he served in a variety of positions, from process engineering management to new product introduction. He holds a BS degree in industrial engineer-

ing from Purdue University, and received his MS in manufacturing systems engineering from Lehigh University.

# **Reviewers Needed**

If you have expertise in a particular technical field and are interested in volunteering as a reviewer for *P&SF*, please contact Dr. James Lindsay, technical editor (techeditor@aesf.org).